Продукты Категория

- FM-передатчик

- 0-50w 50w-1000w 2kw-10kw 10kw +

- ТВ передатчик

- 0-50w 50-1kw 2kw-10kw

- Антенна FM

- ТВ антенны

- Антенна аксессуар

- Кабель соединитель разветвитель питания эквивалентная нагрузка

- RF Transistor

- Напряжение питания

- Аудио оборудование

- DTV Front End оборудование

- система Link

- система STL Система Link Микроволновая печь

- FM-радио

- Сил-о-Метр

- Другие продукты

- Специально для Коронавируса

Продукты Теги

Fmuser Сайты

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> африкаанс

- sq.fmuser.net -> албанский

- ar.fmuser.net -> арабский

- hy.fmuser.net -> Армянский

- az.fmuser.net -> Азербайджанский

- eu.fmuser.net -> Баскский

- be.fmuser.net -> Белорусский

- bg.fmuser.net -> Болгарский

- ca.fmuser.net -> каталонский

- zh-CN.fmuser.net -> Китайский (упрощенный)

- zh-TW.fmuser.net -> Китайский (традиционный)

- hr.fmuser.net -> хорватский

- cs.fmuser.net -> Чешский

- da.fmuser.net -> датский

- nl.fmuser.net -> Голландский

- et.fmuser.net -> эстонский

- tl.fmuser.net -> Филиппинский

- fi.fmuser.net -> финский

- fr.fmuser.net -> Французский

- gl.fmuser.net -> Галицкий

- ka.fmuser.net -> Грузинский

- de.fmuser.net -> Немецкий

- el.fmuser.net -> Греческий

- ht.fmuser.net -> гаитянский креольский

- iw.fmuser.net -> Иврит

- hi.fmuser.net -> Хинди

- hu.fmuser.net -> Венгерский

- is.fmuser.net -> Исландский

- id.fmuser.net -> индонезийский

- ga.fmuser.net -> Ирландский

- it.fmuser.net -> Итальянский

- ja.fmuser.net -> Японский

- ko.fmuser.net -> корейский

- lv.fmuser.net -> латышский

- lt.fmuser.net -> Литовский

- mk.fmuser.net -> македонский

- ms.fmuser.net -> малайский

- mt.fmuser.net -> Мальтийский

- no.fmuser.net -> Норвежский

- fa.fmuser.net -> Персидский

- pl.fmuser.net -> Польский

- pt.fmuser.net -> португальский

- ro.fmuser.net -> Румынский

- ru.fmuser.net -> Русский

- sr.fmuser.net -> сербский

- sk.fmuser.net -> словацкий

- sl.fmuser.net -> словенский

- es.fmuser.net -> Испанский

- sw.fmuser.net -> Суахили

- sv.fmuser.net -> шведский

- th.fmuser.net -> Тайский

- tr.fmuser.net -> Турецкий

- uk.fmuser.net -> украинский

- ur.fmuser.net -> урду

- vi.fmuser.net -> Вьетнамский

- cy.fmuser.net -> валлийский

- yi.fmuser.net -> Идиш

PMOS и NMOS транзисторы

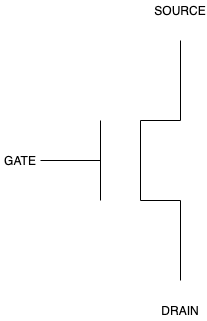

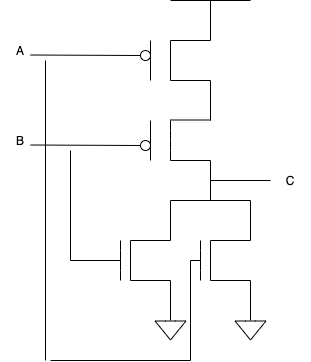

Микропроцессоры построены на транзисторах. В частности, они построены на МОП-транзисторах. МОП — это аббревиатура от Metal-Oxide Semiconductor. Существует два типа МОП-транзисторов: pMOS (положительный МОП) и nMOS (отрицательный МОП). Каждый pMOS и nMOS оснащен тремя основными компонентами: затвором, истоком и стоком.

Чтобы правильно понять, как работают pMOS и nMOS, важно сначала определить некоторые термины:

замкнутая цепь: это означает, что электричество течет от ворот к источнику.

разомкнутая цепь: это означает, что электричество не течет от ворот к источнику; скорее электричество течет от ворот к канализации.

Когда nMOS-транзистор получает напряжение, которым нельзя пренебречь, соединение истока со стоком действует как провод. Электричество будет беспрепятственно течь от источника к стоку - это называется замкнутой цепью. С другой стороны, когда nMOS-транзистор получает напряжение около 0 вольт, соединение истока со стоком будет разорвано, и это называется разомкнутой цепью.

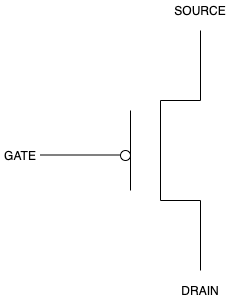

Транзистор p-типа работает точно против транзистора n-типа. В то время как nMOS будет формировать замкнутую цепь с источником, когда напряжением нельзя пренебречь, pMOS будет формировать разомкнутую цепь с источником, когда напряжением нельзя пренебречь.

Как вы можете видеть на изображении pMOS-транзистора, показанном выше, единственное различие между pMOS-транзистором и nMOS-транзистором - это маленький кружок между затвором и первой полосой. Этот кружок инвертирует значение напряжения; Таким образом, если вентиль посылает напряжение, представляющее значение 1, то инвертор изменит 1 на 0 и заставит схему функционировать соответствующим образом.

Поскольку pMOS и nMOS функционируют противоположным образом - взаимодополняющим образом - когда мы объединяем их обе в одну гигантскую схему MOS, это называется схемой cMOS, что означает комплементарный металлооксидный полупроводник.

Использование МОП-схем

Мы можем комбинировать схемы pMOS и nMOS для создания более сложных структур, называемых GATES, а точнее: логических вентилей. Мы уже представили концепцию этих логических функций и связанных с ними таблиц истинности в предыдущем блоге, которые вы можете найти, щелкнув здесь.

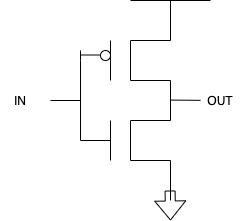

Мы можем присоединить транзистор pMOS, который подключается к истоку, и транзистор nMOS, который подключается к земле. Это будет наш первый пример транзистора cMOS.

Этот cMOS-транзистор действует аналогично логической функции НЕ.

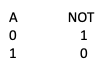

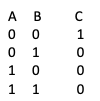

Давайте взглянем на таблицу истинности НЕ:

В таблице истинности НЕ каждое входное значение: A инвертировано. Что происходит с приведенной выше схемой?

Что ж, давайте представим, что на входе 0.

0 входит и идет вверх и вниз по проводу как к pMOS (вверху), так и к nMOS (внизу). Когда значение 0 достигает pMOS, оно инвертируется в 1; Итак, соединение с источником закрыто. Это даст логическое значение 1 до тех пор, пока соединение с землей (дренаж) также не закрыто. Что ж, поскольку транзисторы дополняют друг друга, мы знаем, что транзистор nMOS не инвертирует значение; поэтому он принимает значение 0 как есть и, следовательно, создаст разомкнутую цепь на землю (дренаж). Таким образом, для вентиля создается логическое значение 1.

Что произойдет, если значение IN равно 1? Итак, следуя тем же шагам, что и выше, значение 1 отправляется как на pMOS, так и на nMOS. Когда значение получено pMOS, значение инвертируется в 0; таким образом, соединение с ИСТОЧНИКОМ открыто. Когда значение получено nMOS, значение не инвертируется; таким образом, значение остается равным 1. Когда nMOS принимает значение 1, соединение закрывается; Итак, соединение с землей закрыто. Это даст логическое значение 0.

Объединение двух наборов ввода / вывода вместе дает:

Довольно легко увидеть, что эта таблица истинности в точности совпадает с таблицей, которую производит логическая функция НЕ. Таким образом, это известно как ворота НЕ.

Можем ли мы использовать эти два простых транзистора для создания более сложных структур? Абсолютно! Далее мы построим вентиль ИЛИ-НЕ и вентиль ИЛИ.

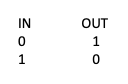

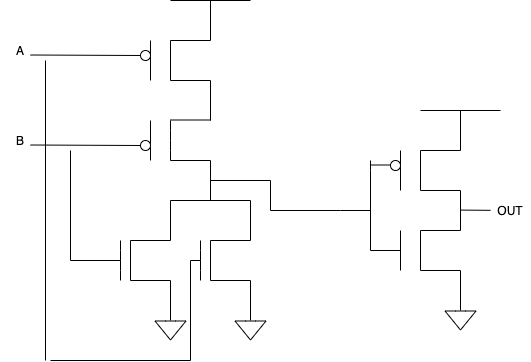

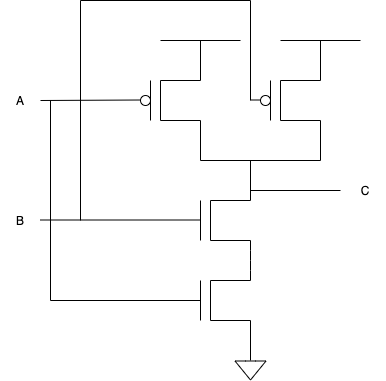

В этой схеме используются два pMOS-транзистора вверху и два nMOS-транзистора внизу. Опять же, давайте посмотрим на вход в гейт, чтобы увидеть, как он себя ведет.

Когда A равно 0, а B равно 0, этот вентиль инвертирует оба значения в 1, когда они достигнут транзисторов pMOS; однако оба транзистора nMOS будут поддерживать значение 0. Это приведет к тому, что затвор будет выдавать значение 1.

Когда A равно 0, а B равно 1, этот вентиль инвертирует оба значения, когда они достигают транзисторов pMOS; таким образом, A изменится на 1, а B изменится на 0. Это не приведет к источнику; поскольку оба транзистора требуют замкнутой цепи для подключения входа к источнику. Транзисторы nMOS не инвертируют значения; таким образом, nMOS, связанный с A, будет давать 0, а nMOS, связанный с B, будет давать 1; таким образом, nMOS, связанный с B, создаст замкнутую цепь на землю. Это приведет к тому, что вентиль выдаст значение 0.

Когда A равно 1, а B равно 0, этот вентиль инвертирует оба значения, когда они достигают pMOS-транзисторов; Итак, A изменится на 0, а B изменится на 1. Это не приведет к источнику; поскольку оба транзистора требуют замкнутой цепи для подключения входа к источнику. Транзисторы nMOS не меняют значения; таким образом, nMOS, связанный с A, будет давать 1, а nMOS, связанный с B, даст 0; таким образом, nMOS, связанный с A, создаст замкнутую цепь на землю. Это приведет к тому, что вентиль выдаст значение 0.

Когда A равно 1, а B равно 1, этот вентиль будет инвертировать оба значения, когда они достигнут транзисторов pMOS; так, A изменится на 0, а B изменится на 0. Это не приведет к источнику; поскольку оба транзистора требуют замкнутой цепи для подключения входа к источнику. Транзисторы nMOS не меняют значения; таким образом, nMOS, связанный с A, будет давать 1, а nMOS, связанный с B, будет давать 1; таким образом, nMOS, связанный с A, и nMOS, связанный с B, будут создавать замкнутую цепь на землю. Это приведет к тому, что вентиль выдаст значение 0.

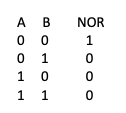

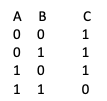

Таким образом, таблица истинности ворот выглядит следующим образом:

Между тем, таблица истинности логической функции ИЛИ-НЕ выглядит следующим образом:

Таким образом, мы подтвердили, что этот вентиль является вентилем ИЛИ-НЕ, потому что он разделяет свою таблицу истинности с логической функцией ИЛИ-НЕ.

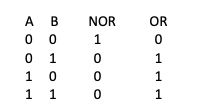

Теперь мы соединим оба гейта, которые мы создали до сих пор, вместе, чтобы создать логический элемент ИЛИ. Помните, что NOR означает НЕ ИЛИ; Итак, если мы инвертируем уже инвертированный гейт, мы вернем оригинал. Давайте проверим это, чтобы увидеть в действии.

Здесь мы взяли вентиль NOR из предыдущего и применили вентиль NOT к выходу. Как мы показали выше, вентиль НЕ принимает значение 1 и выводит 0, а вентиль НЕ принимает значение 0 и выводит 1.

Это примет значения вентиля ИЛИ-НЕ и преобразует все 0 в 1 и 1 в 0. Таким образом, таблица истинности будет следующей:

Если вы хотите попрактиковаться в тестировании этих вентилей, вы можете попробовать указанные выше значения на себе и убедиться, что гейт дает эквивалентные результаты!

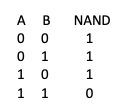

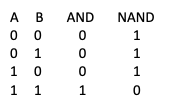

Я утверждаю, что это вентиль NAND, но давайте проверим таблицу истинности этого логического элемента, чтобы определить, действительно ли это вентиль NAND.

Когда A равно 0, а B равно 0, pMOS A выдаст 1, а nMOS A выдаст 0; таким образом, этот затвор будет генерировать логическую 1, поскольку он подключен к источнику по замкнутой цепи и отключен от земли с разомкнутой цепью.

Когда A равно 0, а B равно 1, pMOS A выдаст 1, а nMOS A выдаст 0; таким образом, этот затвор будет генерировать логическую 1, поскольку он подключен к источнику по замкнутой цепи и отключен от земли с разомкнутой цепью.

Когда A равно 1, а B равно 0, pMOS B даст 1, а nMOS B даст 0; таким образом, этот затвор будет генерировать логическую 1, поскольку он подключен к источнику по замкнутой цепи и отключен от земли с разомкнутой цепью.

Когда A равно 1, а B равно 1, pMOS A выдаст 0, а nMOS A выдаст 1; Итак, мы должны также проверить pMOS и nMOS B. PMOS B даст 0, а nMOS B даст 1; таким образом, этот вентиль будет производить логический 0, поскольку он отключен от источника с разомкнутой цепью и подключен к земле с замкнутой цепью.

Таблица истинности выглядит следующим образом:

Между тем, таблица истинности логической функции И-НЕ выглядит следующим образом:

Таким образом, мы убедились, что это действительно вентиль И-НЕ.

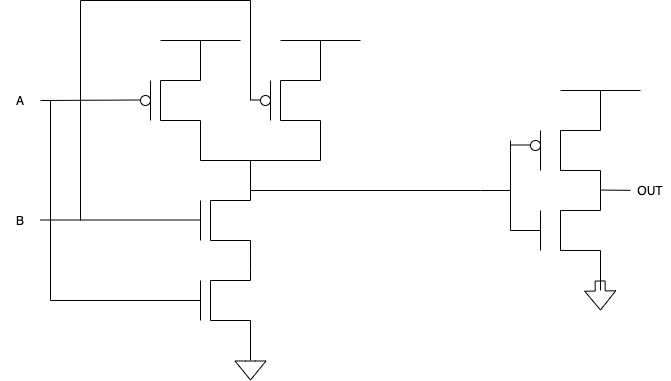

Теперь, как нам построить логический элемент И? Что ж, мы построим ворота И точно так же, как мы построили ворота ИЛИ из ворот ИЛИ! Прикрепим инвертор!

Поскольку все, что мы сделали, применили функцию НЕ к выходу логического элемента И-НЕ, таблица истинности будет выглядеть так:

Опять же, убедитесь, что я говорю вам правду.

Сегодня мы рассмотрели, что такое транзисторы pMOS и nMOS, а также как их использовать для создания более сложных структур! Надеюсь, вы нашли этот блог информативным. Если вы хотите прочитать мои предыдущие блоги, вы найдете список ниже.